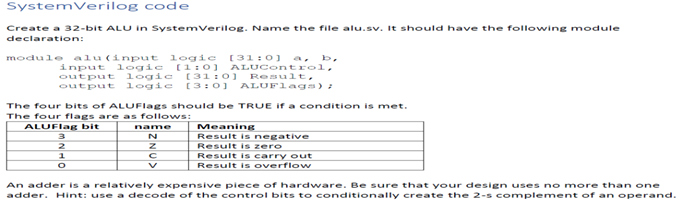

System Verilog Math Functions

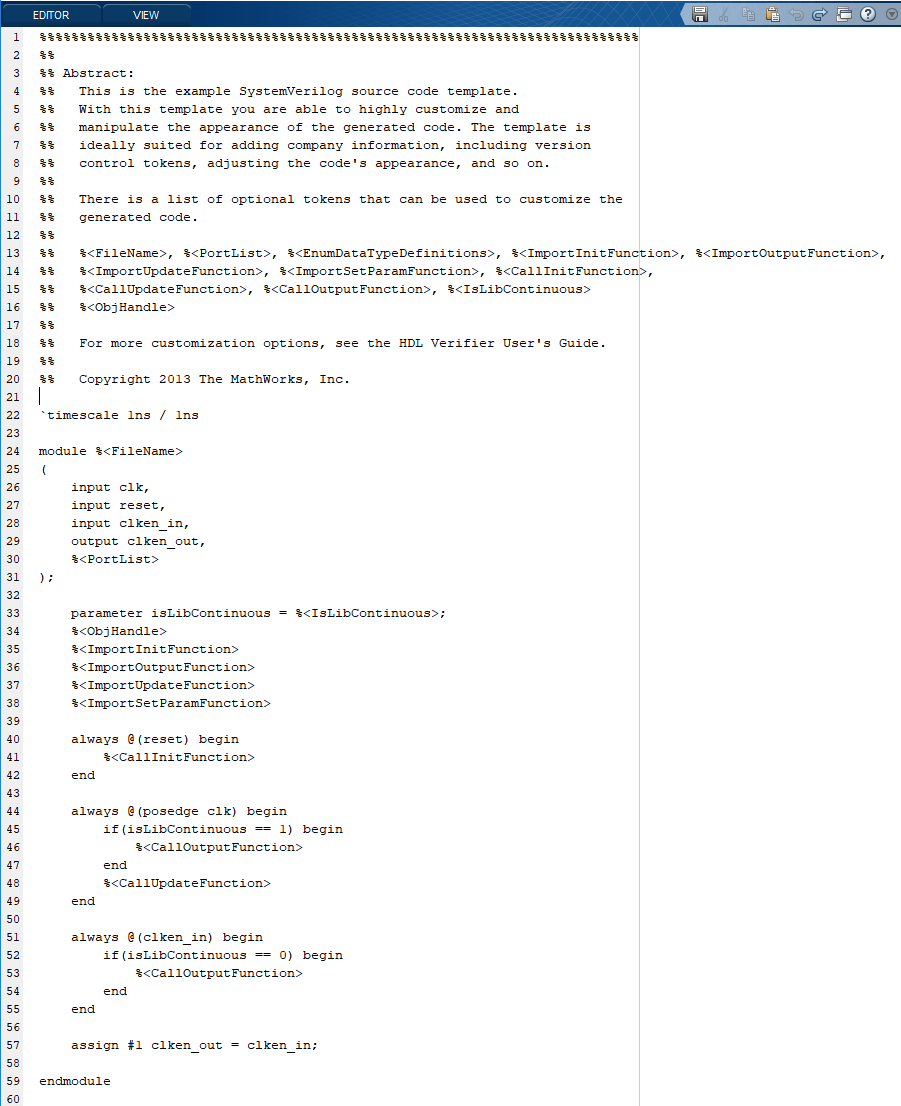

System verilog math functions. On the other hand bad coding style leads to a lot of issues when the code is reused or when it is handed. Each class instance would normally have a copy of each of its internal variables. On calling b_cdisplay if display method in base_class is virtual then extended class display method will get called.

All units have been. For any design verification DV project following best coding practices make life easier for the teammates. Assigning e_c to b_c b_c e_c.

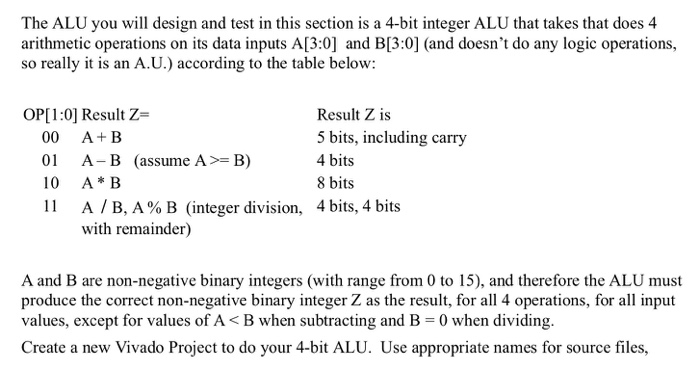

As such it will be a subset of everything verilog knows about. Function new bit 150 ad bit 70 d. The function clog2 returns the ceiling of log 2 of the given argument.

Static functions share the same storage space for all function calls. It can be used in rhs expression of the assign statement or in expressions inside any procedural block. Their usage in verilog is completely different.

SystemVerilog Static Variables Functions. Before that clog2 could be realized as a Constant Function in Verilog 2001. Considering both the classs has the method display.

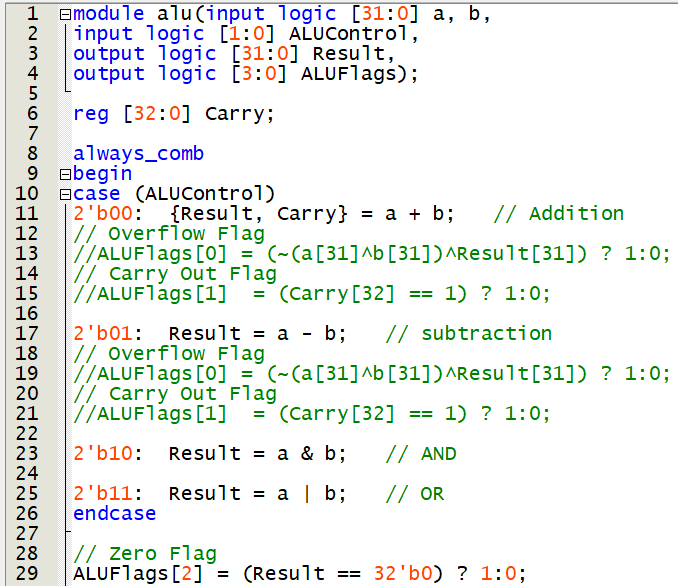

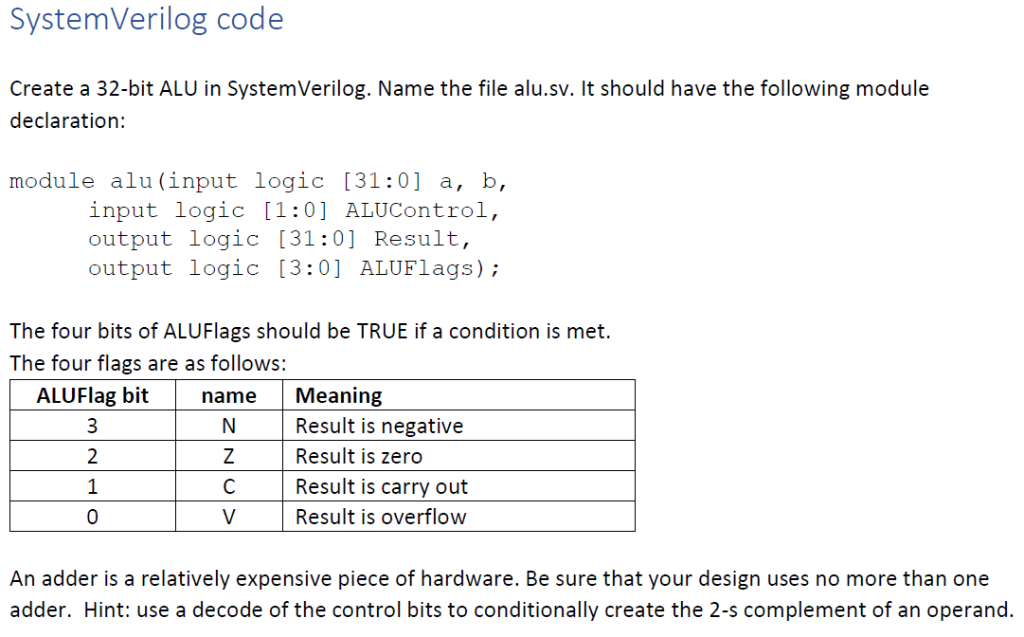

A function cannot have time controlled statements like fork join or wait. Rules for Using Functions in Verilog. For type or non-void functions a value can be returned by adding a final line in code with return abcdWhere abcd is always associated with return and its the expression required to return a value with function callExample below.

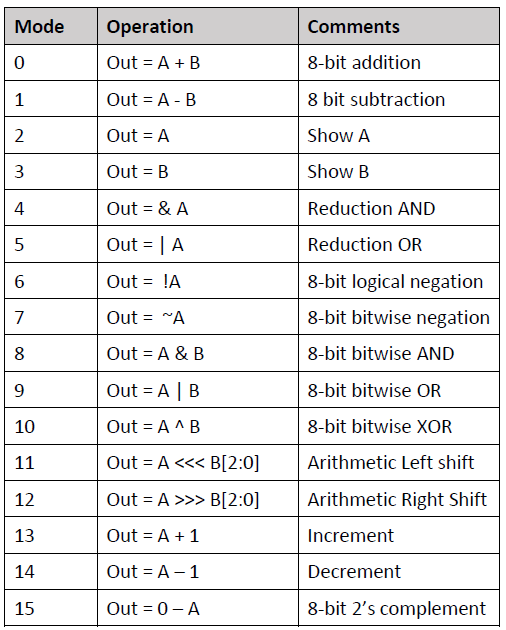

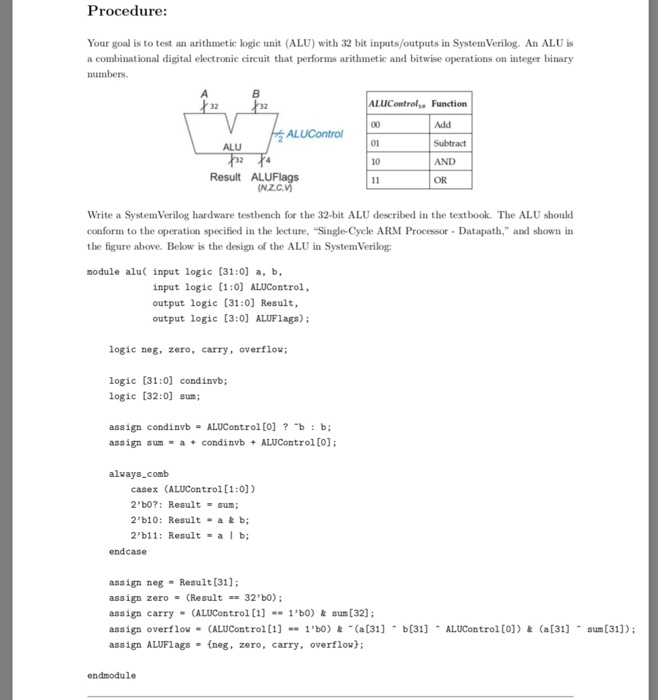

To do this addition using Verilog-1995 constructs we could use the code in Code Example 1. Verilog language itself is clog2 which is a system function.

Following is a sample function that can be used instead for the clog2 function to get a proper output.

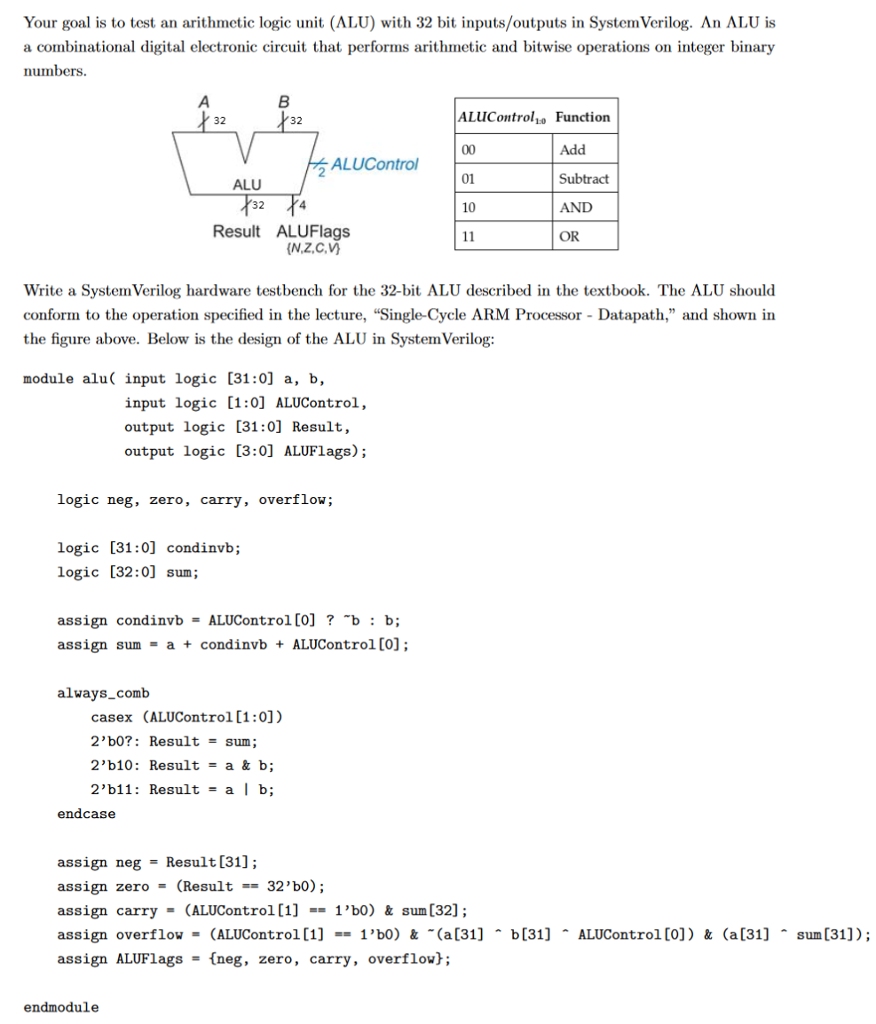

This is typically used to calculate the minimum width required to address a memory of given size. Max returns the element with the maximum value or whose expression evaluates to a maximum. SystemVerilog function can be static. All units have been. This prevents copy and paste errors and allows for more maintainable code. It produces a signal named ready when the quotient output is ready and takes a signal named start to indicate the the input dividend and divider is ready. SystemVerilog functions have the same characteristics as the ones in Verilog. Use functions is a good way to reuse procedural code since modules cannot be invoked from a procedure. Display addr0x0h data0x0h addr data.

Two capabilities in SystemVerilog allow for the creation of a module that can produce a sine wave as an output. The Math function clog2 was incorporated starting from Verilog-2005 IEEE 1364-2005. Functions can only return one value. Module add_signed_1995 input 20 A input 20 B output 30 Sum. The function clog2 returns the ceiling of log 2 of the given argument. Max returns the element with the maximum value or whose expression evaluates to a maximum. Each class instance would normally have a copy of each of its internal variables.

Post a Comment for "System Verilog Math Functions"